Mathis Picot-Digoix soutiendra sa thèse Cifre le vendredi 3 octobre 2025 à 13h30, site de l’ENSEEIHT, salle C002, sur le sujet :

Architectures multi-niveaux et multi-buffers pour la commande rapprochée de composants à semi-conducteurs de puissance en SiC incluant la surveillance de leur état de santé et leur protection en régime extrême dans le domaine de l’aéronautique.

Mathis a réalisé ses travaux dans le cadre des activités de recherche du Groupe CS, en collaboration avec Safran Tech – Saclay et Safran Electrical & Power.

Membres du Jury de soutenance :

- Stéphane Lefebvre, PU, CNAM, Rapporteur,

- Nicolas Ginot, PU, Univ. de Nantes, Rapporteur,

- Hervé Morel, DR, Lab. Ampère Lyon, Examinateur externe,

- Zoubir Khatir, DR, Univ. Gustave Eiffel, Examinateur externe,

- Nathalie Batut, MdC HDR, Univ. de Tours, Examinatrice externe,

- Nicolas Rouger, DR, Laplace, Examinateur interne.

- Frédéric Richardeau, DR, Laplace, Dir. de Thèse,

- Stéphane Azzopardi, Ing. de Recherche Safran Tech Saclay, HdR, Co-Dir. de Thèse,

- Long Thanh Le, Ing. de Recherche Safran Tech Saclay, encadrant industriel de Thèse,

- Hervé Sorel, Ing. de Recherche, Expert Safran Electrical & Power, invité.

Ces travaux s’inscrivent dans un objectif de décarbonation de l’aviation d’ici 2050 par son électrification progressive. Les futurs systèmes électroniques de bord doivent répondre à de nombreuses contraintes : compacité, masse embarquée et fiabilité, et ce dans des conditions extrêmes de fonctionnement. Afin de satisfaire ces contraintes de conception, le MOSFET (Metal Oxide Semiconductor Field Effect Transistor) au carbure de silicium (SiC) apparaît comme un composant semi-conducteur de puissance de choix pour les futurs systèmes de conversion de l’énergie électrique. Il présente des performances énergétiques supérieures à son prédécesseur en silicium, mais cette technologie encore nouvelle en aéronautique doit gagner en maturité et fiabilité pour être adoptée.

Le sujet de thèse est divisible en plusieurs volets. Le premier porte sur la détection et la protection de transistors de puissance MOSFETs SiC en régimes de courts-circuits (CC), et plus globalement en régimes de défaut. Le deuxième concerne sur de la surveillance de l’état de santé, et le dernier explore une compensation des dérives du MOSFET SiC liées à son vieillissement.

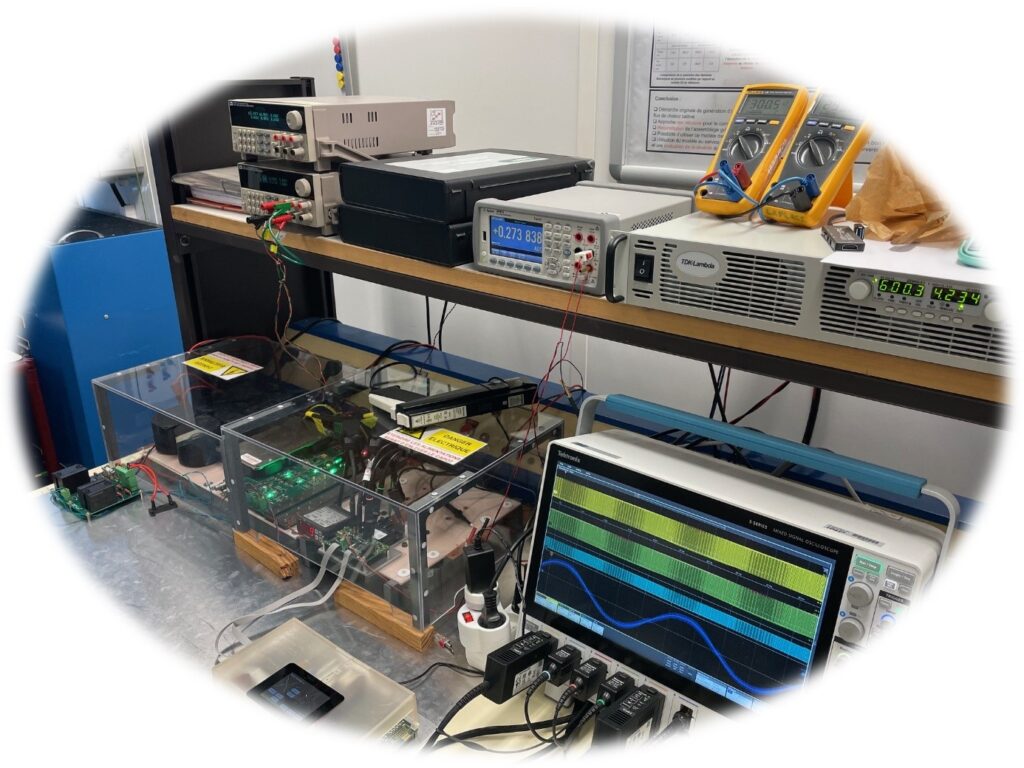

La détection de CC sur MOSFET SiC repose généralement sur la surveillance de la tension ou du courant de drain. Ici, une approche basée sur la tension de grille (Vgs) est proposée, facilitant l’intégration (niveau de tension, empreinte PCB, immunité aux perturbations). Une commande innovante à voies parallèles optimise les durées de protection : une faible résistance de grille (10 Ω) est utilisée en commutation, tandis qu’une forte résistance (1 kΩ) en conduction rend la grille sensible aux CC. Un seuillage de Vgs permet alors leur détection. Les tests ont révélé deux protections supplémentaires, contre des surintensités modérées et des dégradations de l’oxyde de grille. Validée expérimentalement sur MOSFETs SiC discrets et sur modules multi-puces 600V/150A, cette méthode assure une protection contre CC en 150 ns.

Le deuxième volet concerne la surveillance de l’état de santé du MOSFET SiC en réutilisant l’architecture de commande rapprochée à voies parallèles. Deux méthodes ont été développées, exploitant une voie de commande à forte résistance de grille pour réaliser un amorçage ponctuel très ralenti du transistor au sein d’une trame de commande. Cela permet d’obtenir une forme d’onde de Vgs peu bruitée, utilisée pour extraire des indicateurs de vieillissement.

- Méthode numérique : numérisation entrelacée à haute résolution d’une portion de Vgs afin d’en extraire trois indicateurs (tension et durée du plateau Miller, tension de seuil).

- Méthode analogique : mise en évidence d’un creux de tension sur Vgs, un phénomène électrique inédit au niveau de l’état de l’art et découvert durant la thèse, apparaissant sous amorçage ralenti sur la courbe d’amorçage de Vgs. Ce creux, sous faible tension de commande, se rapproche de la tension de seuil (Vth), un paramètre clé habituellement très difficile à mesurer avec précision en fonctionnement. Son extraction est réalisée par un circuit de mémorisation de creux analogique dédié.

Ces deux méthodes ont été validées en fiabilité (précision et répétabilité) à 0,3 % près et fonctionnalité sur banc de puissance en régime nominal sur des MOSFETs SiC discrets.

Le troisième volet s’inscrit dans la continuité du précédent et explore une compensation active des dérives du MOSFET SiC liées à son vieillissement. De nouvelles architectures de commande à topologie série multi-niveaux ont été développées afin d’introduire un nouveau niveau de tension de commande fortement négatif. Ce niveau permet de dépiéger efficacement les charges accumulées progressivement dans la couche d’oxyde de grille, et de ramener le MOSFET à un état de santé acceptable.

L’ensemble de ces travaux contribue à l’amélioration de la fiabilité et de la durée de vie des MOSFETs SiC, favorisant leur intégration dans les futures applications aéronautiques.

Compilation de la production scientifique et des brevets d’invention déposés sur HAL :

https://hal.science/search/index/?q=mathis+picot-digoix&rows=30&sort=publicationDate_tdate+desc