Soutenance de thèse – Luc BIMMEL – Vendredi 20 février à 09 h 00 – Salle des thèses C002, ENSEEIHT

Luc BIMMEL soutiendra sa thèse le vendredi 20 février 2026 à 09 h 00 en salle des thèses de l’ENSEEIHT (Amphi C002), au 2 Rue

Responsable de groupe : Marc COUSINEAU

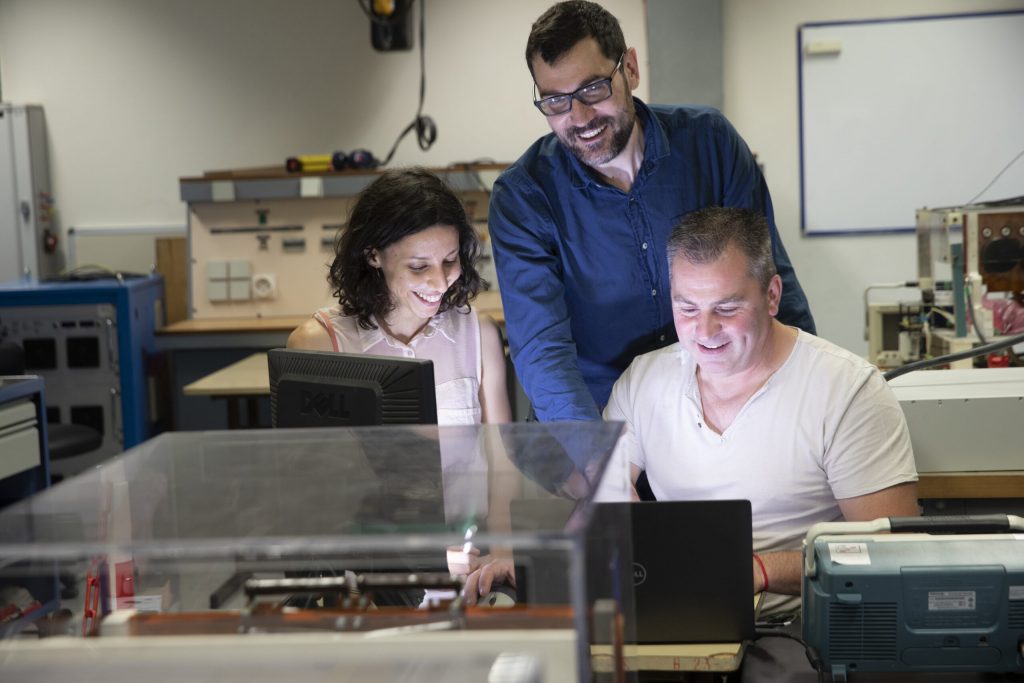

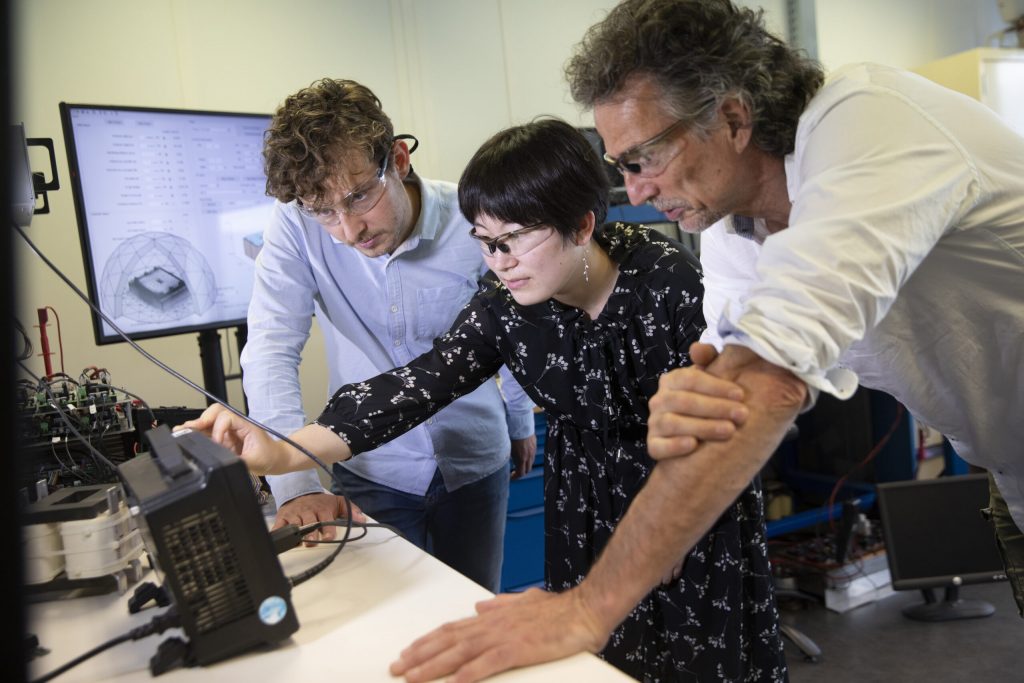

Le groupe Convertisseurs Statiques est basé sur le site N7 et développe à partir du concept de cellule de commutation des recherches selon 2 grandes thématiques qui sont d’une part le développement et l’utilisation de nouvelles topologies de convertisseurs multiniveaux et d’autre part l’intégration de puissance avec comme objectif un haut rendement et une forte densité de puissance.

Mots clés :

Ces deux thématiques transversales nous ont conduit à structurer notre équipe selon 4 opérations de recherche :

OP1 : Architectures de forte puissance, applications réseaux d’énergie et pilotage numérique de structures hybrides complexes

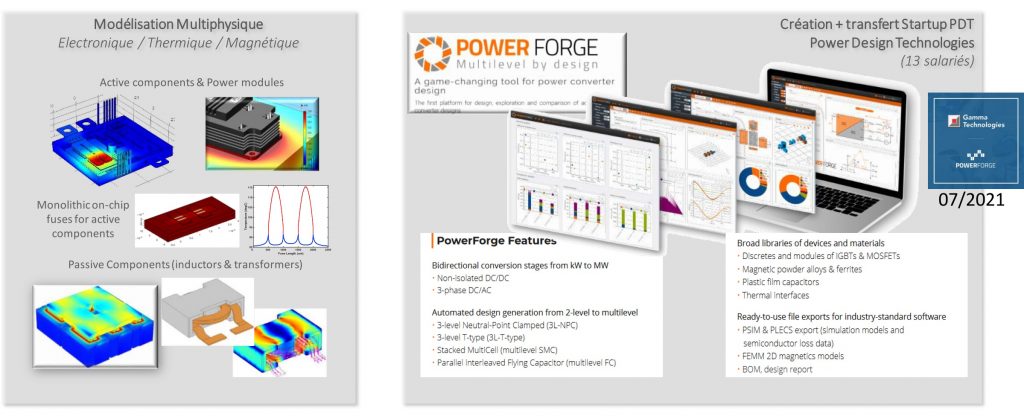

OP2 : Méthode et outils pour le dimensionnement optimisé et le prototypage virtuel en Electronique de puissance

OP3 : Intégration de Puissance et Efficacité Energétique : Composants grands gaps et ultra grands gaps, et Gate drivers intégrés

OP4 : Amélioration de la Fiabilité Fonctionnelle Globale des Semi-Conducteurs de Puissance à Grand-Gap par de multiples approches

Nos objectifs scientifiques sont principalement focalisés sur :

– le développement et l’optimisation des fonctions de conversion multi-cellulaires de très fortes puissances,

– la conception de cellules de commutation et d’architectures hautement intégrées.

ayant en ligne de mire des applications où l’efficacité énergétique ainsi que la densité de puissance sont critiques.

La détection de défaut et/ou dégradations en régime extrême, la protection et la reconfiguration en vue de la garantie de service et/ou de fonction sont aussi des éléments transverses. Nous intervenons de la puce de puissance (GaN, SiC, Diamant, que nous contribuons à concevoir, analyser et caractériser) au convertisseur forte puissance dans son environnement, avec des réalisations à l’échelle 1. Ceci inclut aussi la réalisation de circuits intégrés ultra rapides en technologie BiCMOS pour la commande rapprochée, la mise en œuvre de méthodologies de simulation multi-physique pour l’analyse fine des limites d’usage des puces en mode de court-circuit et la conception par optimisation de topologies multi-cellulaires.

Nos activités de recherche couvrent les problématiques de la conversion d’énergie électrique et reposent sur la combinaison d’approches théoriques et expérimentales autour de la notion de cellule de commutation.

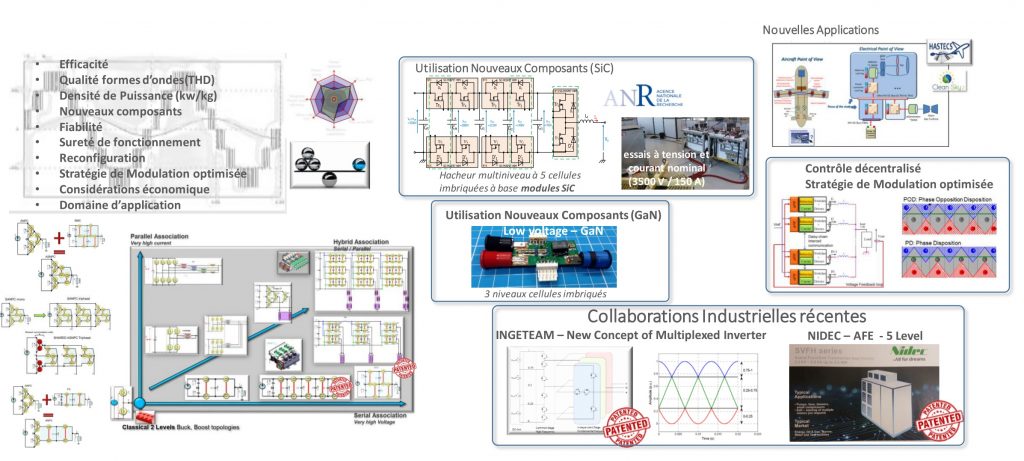

Le groupe s’est spécialisé dans l’étude de nouvelles structures de convertisseurs multicellulaires de moyenne et de forte puissance (du kW au MW) mettant en jeu des agencements originaux des cellules de commutation imbriquées séries, superposées parallèles et la parallélisation globale ou partielle par des dispositifs innovants de couplages magnétiques. Ces agencements, considérés seuls ou mixés, sont mis à profit pour produire des formes d’ondes multiniveaux à haute fréquence apparente permettant de réduire le coût du filtrage sur une très large gamme de besoins :

Ceci en intégrant les contraintes spécifiques à ces domaines dès la phase de conception.

La validation de ces nouvelles structures de conversion nécessite le développement de contrôles analogiques et numériques rapides, capables d’observer et de gérer l’ensemble des variables d’état internes. Cette validation passe systématiquement par une phase de réalisation expérimentale à un niveau de puissance significatif. Cela implique de traiter des problématiques complexes de connectique, de gestion thermique, d’assemblage tridimensionnel et d’intégration de la commande (ASIC, FPGA, HIL). Des outils de simulation, de co-simulation et d’optimisation sont développés, adaptés et couplés afin de déterminer les meilleurs compromis globaux lors des phases de dimensionnement et de conception du contrôle rapproché (MLI).

Ces travaux sont complétés par des études sur la robustesse des composants de puissance et l’analyse de leurs modes de défaillance, en lien avec la topologie des circuits. Ces recherches aboutissent à la définition de nouvelles structures plus sûres, dotées de propriétés de tolérance aux pannes.

Enfin, le groupe CS mène des recherches en électronique de puissance afin de contribuer à l’avancement et à l’acquisition de nouvelles connaissances dans ce domaine, avec pour objectif leur valorisation à travers des partenariats industriels portant sur des enjeux sociétaux majeurs liés à la gestion de l’énergie électrique (efficacité, conversion, intégration, fiabilité, etc…).

Cette démarche s’articule autour de deux axes principaux :

– Développer, étudier ou améliorer de nouvelles technologies, topologies ou méthodes, en s’appuyant sur des moyens propres ou des financements publics. Ces travaux visent à innover et à faire progresser le front des connaissances dans notre domaine.

– Assurer le transfert et la valorisation de ces avancées grâce à des partenariats industriels, que ce soit sous forme de contrats directs ou dans le cadre de projets nationaux et internationaux. Cette dynamique favorise une collaboration étroite avec les industriels et peut conduire à la création de start-up.

Anne Castelan, Didier Flumian et Nicolas Rouger – Transformateur électronique de forte puissance à base de composants SiC :

Yuying Shi, Maxime Pain et Thierry Meynard- Validation de procédures de dimensionnement de tranformateur intercellules :

Les recherches menées dans le cadre de cette opération concernent principalement le développement et la conception de convertisseurs multicellulaires avec comme objectif, par l’association de cellules de commutation élémentaires ou association de convertisseurs, l’optimisation de l’efficacité énergétique ainsi que l’optimisation des formes d’ondes. Les topologies multicellulaires permettent d’améliorer les performances des convertisseurs au prix d’une plus grande complexité, avec plus de semi-conducteurs et l’ajout de composants passifs (condensateurs) au cœur de la cellule de commutation.

Concernant nos travaux récents :

Pour des applications en moyenne tension, dans les structures triphasées, une mutualisation de certains éléments est possible. Ce principe innovant a été appliqué

– pour l’étude d’une topologie Common Flying Capacitor (CFC) où des cellules de commutation et des condensateurs flottants sont mutualisés entre les trois phases d’un onduleur triphasé. Cette mutualisation permet de réduire le nombre de composants et d’augmenter ainsi la densité de puissance du convertisseur tout en conservant les avantages des topologies multiniveaux, ce qui est primordial pour l’électrification des transports aérien ou terrestre.

– et pour l’étude d’une topologie d’onduleur triphasé moyenne tension, la concentration des contraintes de découpage au sein d’un bras mutualisé permettant de réaliser des variateurs de vitesse 4,16kV et 6,6kV en associant des composants 1,7kV qui commutent à plusieurs kHz avec des composants 4,5kV ou 6,5kV qui ne font qu’aiguiller la puissance à 50Hz.

Ainsi, l’utilisation de composants basse tension permet d’améliorer le rendement et de réduire sensiblement les coûts. Ces nouvelles topologies, bien qu’efficaces pour réduire la quantité d’énergie stockée et le nombre de composants actifs, posent des défis en termes de commande et de régulation, notamment pour maintenir constantes les tensions des condensateurs flottants. Des stratégies de contrôle adaptées ont été élaborées, comme notamment la commande décentralisée/distribuée de convertisseurs multicellulaires, aujourd’hui mise à profit dans le cadre d’un projet européen dédié (projet Horizon-Europe SCOPS).

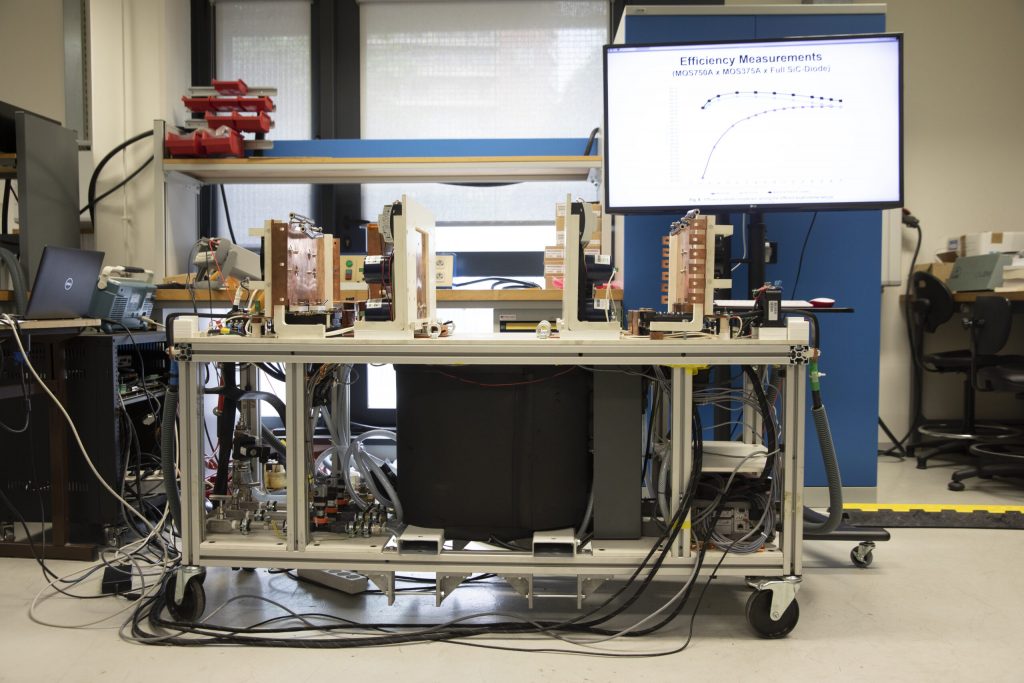

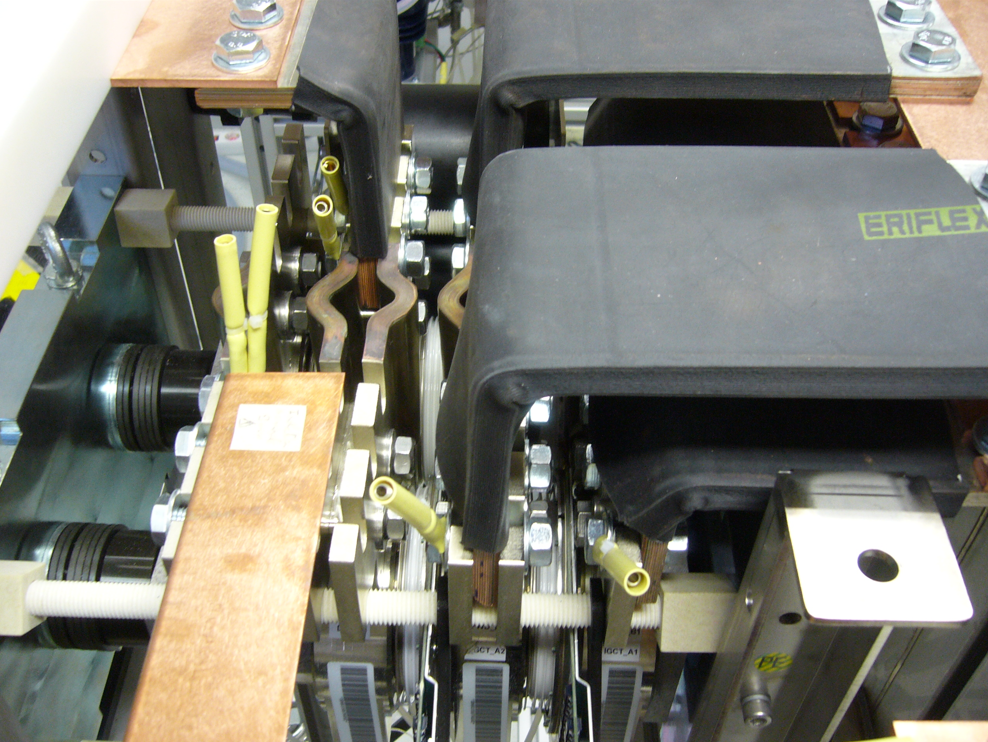

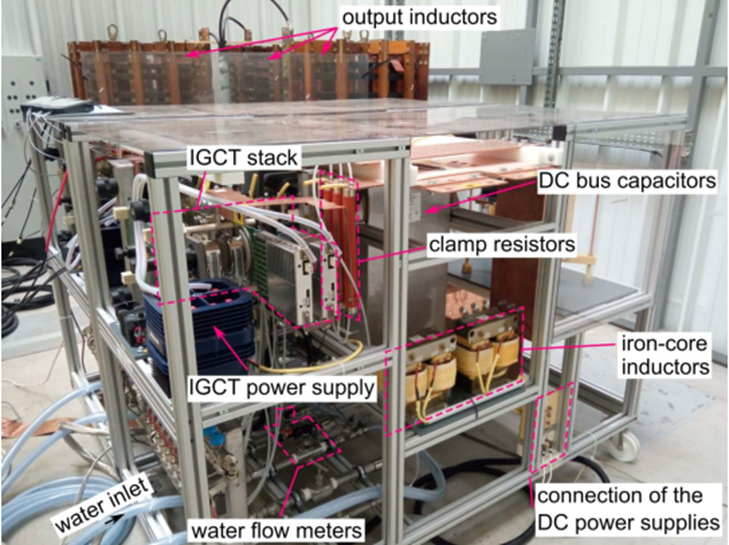

Dans les stations de conversion AC/DC pour les réseaux HVDC, la topologie MMC (Modular Multilevel Converter) est aujourd’hui largement utilisée. Dans la gamme de puissance du GW, le choix des composants semi-conducteurs de la cellule élémentaire est essentiel pour maximiser le rendement. Nos travaux ont permis de démontrer la pertinence des IGCT (Thyristor blocable) dans ce type d’application, remettant ainsi en cause le choix de l’IGBT fait par de grands groupes industriels. Un modèle électrothermique a été développé au laboratoire afin de déterminer avec précision les pertes et les températures de jonction dans chaque semi-conducteur constituant une branche de MMC. Suite à cette étude, un banc d’essais en régime permanent, constitué de deux cellules à base d’IGCT mises en opposition, a été conçu et mis en œuvre afin de valider le modèle électrothermique. Avec une tension de bus DC allant jusqu’à 5 kV et des courants dépassant 2 kA, des composants 4,5 kV et 10 kV ont été testés dans des conditions de fonctionnement équivalentes à celles d’une station de conversion d’une puissance de 1 GW.

Transformateur électronique de forte puissance à base de composants SiC :

Banc de mise en opposition de deux cellules à IGCT :

Les architectures de conversion multicellulaires sont une spécialité reconnue de l’équipe ; elles ont donné lieu à plusieurs transferts réussis vers l’industrie, tout d’abord en Moyenne Tension et Forte Puissance (1-10kV, 1_10MW) et se sont ensuite propagées dans des domaines de tension et de puissance de plus en plus basse, les plus récentes concernant les alimentations internes de nos téléphones portables (1-5V, 1-10W).

En parallèle, la révolution des composants semiconducteurs de puissance à grand gap est venue bouleverser notre discipline et a permis d’espérer des améliorations de nos systèmes.

Entre les architectures série, parallèle, ou hybrides qui permettent de mettre en compétition des composants de calibre de tension et de courant différents, et le choix entre composants Si ‘classiques’ ou grand gap, les concepteurs disposent donc aujourd’hui d’un nombre augmenté de degrés de liberté, mais aucune hiérarchie immuable ne peut être établie en ce domaine. Des méthodes et outils spécifiques doivent donc être développés pour assister la conception des convertisseurs de demain.

Notre équipe a toujours accordé beaucoup d’attention à décrire de manière précise les principes fondamentaux qui régissent notre discipline (comme en attestent nos contributions aux techniques de l’ingénieur) et cette démarche est finalement à la source de nos recherches récentes et actuelles sur les méthodes d’étude et de conception. Le développement d’un formalisme unifié faisant de l’électronique de puissance classique un cas particulier des convertisseurs multicellulaires nous a permis de développer des modèles génériques permettant de comparer rapidement des solutions faisant appel à des technologies différentes (interrupteurs Si, SiC ou GaN, composants à montage de surface ou piqués, composants discrets ou modules, circuit imprimé ou busbar, etc..). La liste des critères de comparaison traditionnels (rendement, masse, coût) peut être enrichie avec des critères plus actuels prenant en compte le développement durable (utilisation de matières premières, empreinte CO2, analyse de cycle de vie, …).

Lien de démonstration : http://power-conversion.enseeiht.fr/

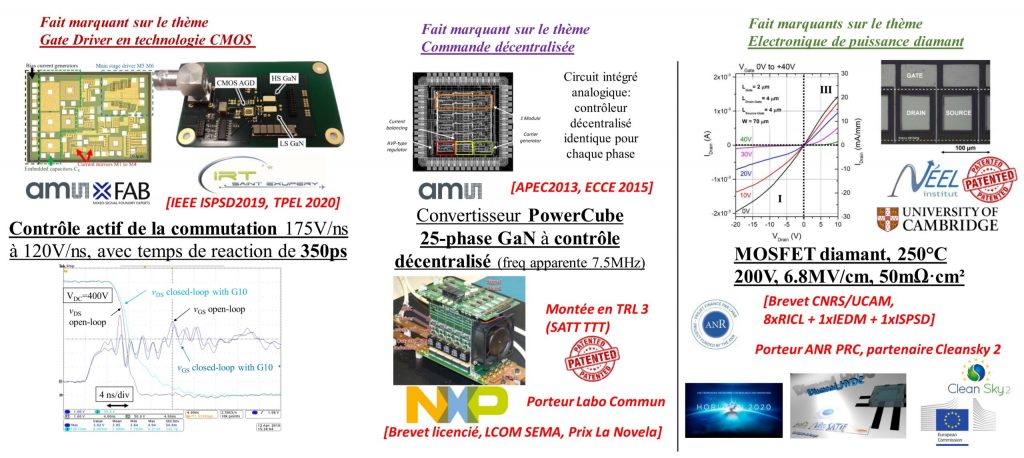

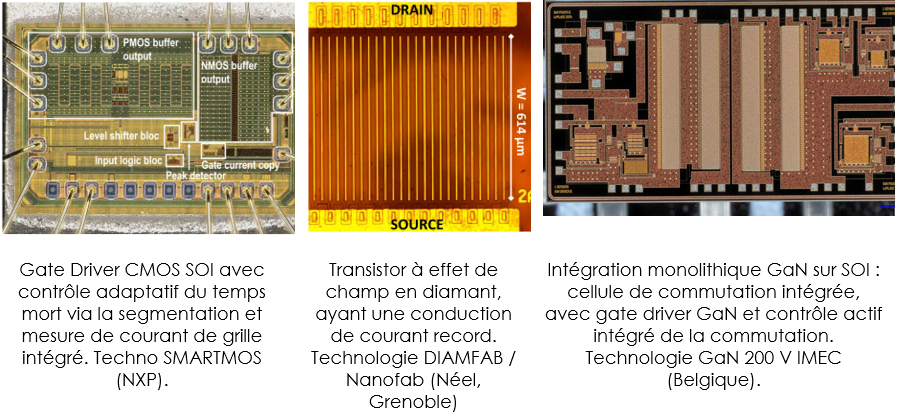

Pour atteindre les performances les plus élevées des convertisseurs, il est nécessaire de maîtriser les nouvelles technologies telles que l’intégration microélectronique CMOS, les technologies GaN et ultra grands gaps (Diamant). Cette opération a pour but de concevoir et caractériser des nouvelles architectures de circuits Gate Drivers en technologie CMOS, pour le pilotage de transistors et modules GaN et SiC, ainsi que de concevoir la prochaine génération de fonctions intégrées et composants de puissance en technologies GaN et diamant. Notre groupe ne dispose pas de centrale technologique « in house », mais a accès à tous les outils de conception, simulation et fabrication de telles technologies de pointe, via nos partenariats et notre expertise. Cette maitrise des outils nous permet de proposer des fonctionnalités impossibles à réaliser via une association de composants discrets, ainsi que de mettre au point les composants et cellules de commutation de la prochaine génération. Notre expertise est donc de pouvoir concevoir ces fonctions, à l’échelle inférieure au µm et au µA, pour les implémenter et les démontrer sur des cellules de commutation de puissance, à l’échelle macroscopique et au-delà de plusieurs centaines d’Ampères et centaines de Volts.

Circuits Gate Driver en technologie CMOS pour composants de puissance GaN et SiC : L’optimisation de la commutation des transistors grands gaps est une réelle difficulté : les fortes vitesses permettent de réduire les pertes par commutation, mais engendrent des sources de perturbation électromagnétique à amplitudes et fréquences élevées. Nous avons proposé des stratégies de contrôle actif de la commutation, notamment par un rebouclage de la partie puissance sur la partie commande, afin de réduire uniquement la séquence de commutation de dV/dt, pour améliorer les compromis CEM/pertes. Ceci est particulièrement difficile avec les transistors GaN moyenne tension, pouvant commuter 400 V en l’espace de quelques ns. Une intégration sur circuit CMOS permet alors, via une optimisation et une bande passante analogique proche de 10 GHz, de réduire le courant de grille uniquement pendant la phase de dV/dt, via un rebouclage et une amplification analogique. Grâce au LabCom SEMA, d’autres solutions de circuits intégrés dans la technologie SmartMOS de NXP sont mises au point, afin d’optimiser et de contrôler de façon adaptative le temps mort de cellules SiC, ou, en lien avec l’opération 4 de notre groupe, d’améliorer la détection et protection des régimes extrêmes de court-circuit.

Electronique de puissance Diamant, intégration monolithique GaN, SiC et diamant : les composants grands gaps SiC et GaN sont commercialisés depuis de nombreuses années, et apportent des ruptures dans les performances des convertisseurs. Cependant, les matériaux ultra grands gaps tels que Ga2O3, h-BN, AlN, ZnOx et diamant sont identifiés comme la prochaine génération de rupture. Le diamant est celui qui est qualifié « d’ultime », grâce à ses spécificités. Cette activité amont, est principalement portée par des laboratoires et start-up avec lesquels nous collaborons étroitement (Institut Néel, DIAMFAB, Univ. of Cambridge, U. Cadiz, Arizona State University, AIST). Nos contributions ont été saluées via notre participation à 2 projets européens, 1 PEPR (Frenchdiam), 2 ANR dont une coordination, et le trophée des Etoiles de l’Europe du projet GreenDiamond, ainsi que plusieurs autres projets européens déposés sur la période. S’appuyant sur la collaboration très étroite avec l’Institut Néel et la start-up DIAMFAB, des avancées importantes sont obtenues, vers une cible 1 kV, 1 A. D’autre part, l’intégration monolithique permet de réduire drastiquement les éléments parasites d’interconnexion entre les composants de puissance et leurs organes de commande rapprochée. La technologie GaN latérale permet cette intégration. Nous concevons et réalisons actuellement des fonctions intégrées de commande en technologie GaN sur SOI, via Europractice et la technologie IMEC (Belgique).

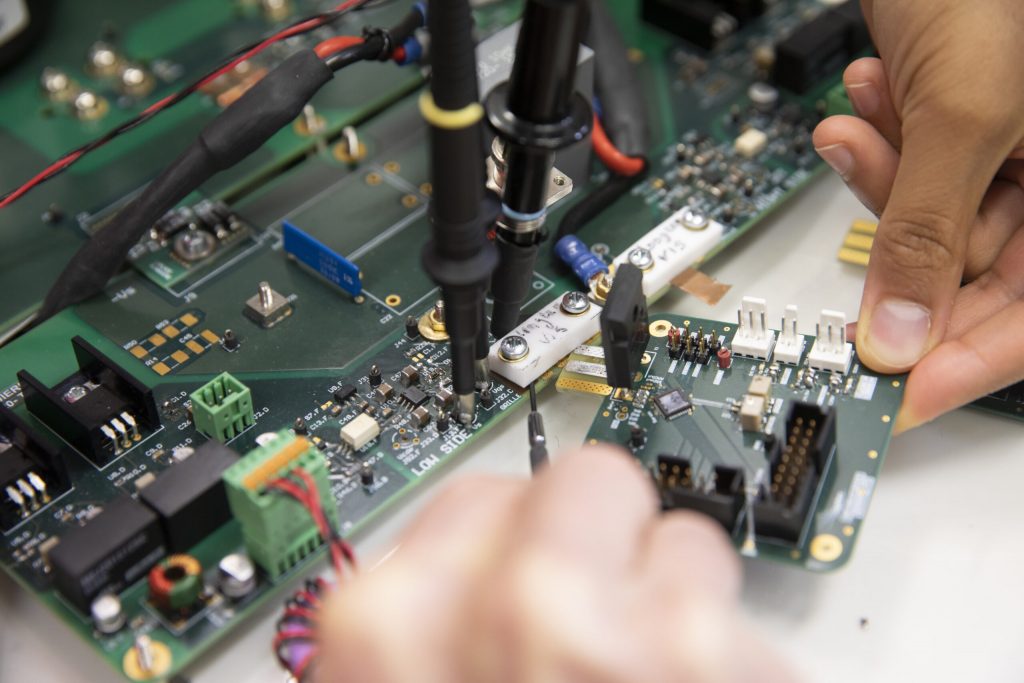

Banc de caractérisation électrique de composants à granp gap en régime extrême de fonctionnement et circuit intégré de commande rapprochée associé.

De multiples approches originales et impactantes : Architectures Gate-Driver Innovantes, Technologies d’Intégration sur Puce et Modélisation Multi-Physique Approfondie des Mécanismes de Défaillance.

Consacrée en grande partie à la recherche de nouvelles topologies à tolérance de panne jusqu’en 2016 – 2017, cette opération a profondément évolué thématiquement et sur le fond pour revenir « aux sources » sur des sujets relevant globalement de l’amélioration de la fiabilité des semi-conducteurs à grand-gap du point de vue de leur usage incluant en priorité l’étude les régimes extrêmes accidentels.

En effet, la pénétration des technologies MOSFET SiC et du HEMT GaN est encore très marginale dans les applicatifs critiques et à longue durée de vie (ex. ferroviaire et aéronautique) en raison d’une fiabilité intrinsèque réduite et mal connue et des niveaux de qualification très exigeants y compris sur la tenue au court-circuit.

Face à cette problématique nos recherches visent, en « aval », à proposer des solutions originales de « compensation » par le gate-driver (§4.1) et d’intégration sur puce (§4.2) ; et en « amont » à caractériser finement les limites d’usage par la mise en place d’une démarche complète et approfondie de modélisation multi-physique des mécanismes de défaillance sur stress fonctionnels ciblés et aggravés (§4.3). Les faits « marquants » sont présentés dans la suite sur la période 2019 – 2024 :

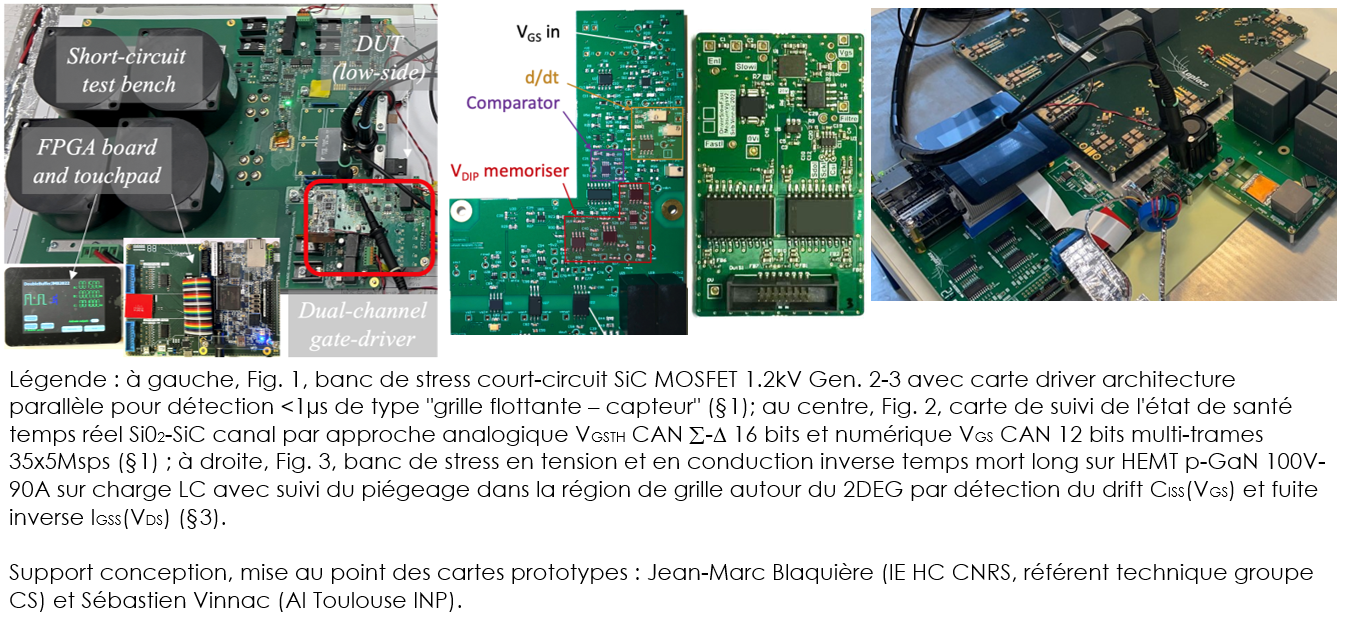

4.1 Architecture multi-fonctionnelle de gate-driver pour la surveillance en temps réel de l’état de santé des puces de puissance SIC MOSFET et leur protection en court-circuit.

Nos travaux ont été centrés sur une architecture de gate-driver générique et multi-fonctionnelle de type segmentée parallèle à résistances de grille sélectives commutées. Sur MOSFET SiC deux nouveaux concepts ont émergé :

– d’une part « la grille flottante – capteur » entre les commutations, offrant une haute sensibilité de détection « sub-µs » du courant de fuite thermique de grille en court-circuit de type 1 (dépolarisation naturelle de VGS avec mode de défaillance ultime fail-to-open) ainsi qu’une détection du di/dt de défaut en type 2 (surpolarisation naturelle de VGS par effet Miller). La Fig. 1 montre le banc de test sur lequel ce premier concept a été validé en composant discret et aussi sur module fort courant.

– d’autre part « la commutation d’amorçage ultra-ralentie » permettant de manière ponctuelle et peu intrusive, en temps réel, d’extraire de multiples indicateurs d’état de santé de l’interface oxyde Si02 – SiC dans la région critique de canal. Une approche dédiée d’auto-échantillonnage analogique de VGSTH sous faible polarisation de grille (nouvelle méthode dite du « creux » de VGS) et une approche générique de numérisation multi-trame haute résolution de VGS ont été développées et comparées à l’aide de nombreux développement expérimentaux présentés en Fig. 2. Ces deux techniques innovantes ont donné lieu à des résultats remarquables de précision et de répétabilité à 0.5% près sur onduleur MLI 600V – 20kHz. (Réf. thèses F.Boige – collaboration univ. de Nottingham et Naples – 2019, M.Picot-digoix – 2024, post-docs Y.Barazi – IRT SE et W.Jouha 2021, 4 brevets dont 2 en montée TRL en collaboration avec Safran Tech, nombreuses distinctions).

Tara Niakan et Frédéric Richardeau – Banc de caractérisation électrique de composants à granp gap en régime extrême de fonctionnement et circuit intégré de commande rapprochée associé.

4.2 Conception et développements technologiques pour une intégration ultime à haute fiabilité.

En lien étroit avec l’opération 3 du groupe CS, les concepts précédents, en particulier sur la gestion du court-circuit, ont été adaptés et enrichis en tirant parti d’une intégration du gate-driver sur ASIC CMOS offrant des niveaux de rapidité, de précision et d’immunité bien supérieurs à l’intégration CMS réalisée en §4.1.

Des résultats tout aussi remarquables ont été obtenus sur module MOSFET SiC très fort courant en double pulse 800V avec des délais de protection de quelques centaines de ns seulement et une haute robustesse sur la variabilité du point de fonctionnement (Thèse A. El Boubkari – 2024 – LabCom SEMA).

En collaboration étroite (et historique) avec l’équipe ISGE du LAAS, les travaux amont d’intégration monolithique verticale de cellule de commutation se poursuivent pour miniaturiser et fiabiliser les puces par la réduction du nombre d’interconnexions. Ce thème a évolué vers des structures multi-pôles en SiC combinant diodes JBS, VD-MOSFET et de nombreuses nouvelles briques technologiques en cours d’étude par le L2n (leader) et le LAAS : implantation p+ profonde, isolation semi-traversante par gravure haute énergie, via métallique enfouis de reprise de contact face arrière – face avant de la puce (ANR PRC MUS²-IC – 2022 – 2026 – Portage et animation : Laplace groupe CS).

4.3 Modélisation multi-physique des mécanismes de défaillance sur stress fonctionnels ciblés et aggravés.

En relation directe avec l’opération 2 du groupe CS, sous un angle plus méthodologique et tirant parti d’un fort capital de résultats expérimentaux et d’expertise issus du §4.1, une démarche complète (mais complexe et ardue) de modélisation multi-physique sous Comsol™ 2D d’une puce SiC MOSFET en régime de court-circuit a été initiée en 2020. Les temps et énergies critiques de début de fusion d’électrode de source et de fissuration d’oxyde de protection de grille peuvent être extraits permettant de spécifier les marges de temps de protection du gate-driver afin que la puce puisse résister à des court-circuits répétés sans (trop) subir de dégradations métallurgiques et thermo-mécaniques (post-doc de M.Shqair 2023 – 2024 – Financement sur fonds propres groupe CS, 1er Prix des Best Paper Awards ESREF’23, conf. sur invitation IEEE IRPS’24 USA).

Une démarche analogue transposée au HEMT GaN basse tension est a été initiée courant 2024 à travers une collaboration supplémentaire avec le groupe ISGE du LAAS (thèse en cours de Mme N.Essobai) et en appui avec les résultats expérimentaux issus de la thèse de L.Ghizzo (2022 – 2024).

La Fig. 3. montre un des bancs de caractérisation réalisé en lien avec Thales et le CNES. De nouveaux facteurs de stress et mécanismes de dégradation associés ont été identifiés sur la région de grille p-GaN et seront prochainement simulés sur TCAD Sentaurus™ puis liés à Comsol™.

Le groupe Convertisseurs Statiques dispose d’outils de conception de prototypes, ainsi que le test des convertisseurs (4 x 15kVA, 2 x 25kVA, 1 x 60kVA, 1 x 100kVA, Raccordement 150kW et charge 50kVA), incluant la génération de la commande (numérique, analogique, HIL) et la conception et la caractérisation de circuits intégrés CMOS utiles pour la commande rapprochée et éloignée des cellules de commutation ou convertisseurs de puissance.

Le groupe Convertisseurs Statiques est fort de nombreux partenaires industriels et universitaires :

Industriels : AIRBUS, ALSTOM et Transport Plate-forme PRIMES, CIRTEM, HELION, LIEBBHER Aerospace, S2M, SCHNEIDER ELECTRIC-APC, SNCF-Direction de l’Ingénierie, NXP semiconductors, TECHNOFAN, RENAULT-TECHNOCENTRE, VALEO, ZODIAC, RONGXIN POWER ELECTRONIC Co, …

Universitaires : G2ELAB, LAAS ; SATIE, Insitut Néel, University of Cambridge, GRUCAS (Université Fédérale Santa Catarina, Brésil), LEEPCI (Université Laval, Quebec), Ecole Nationale d’Ingenieurs de Tunis – LSE, PowerLab (Université technique fédérale Santa Maria Valparaíso, Chili), IES, …

Le groupe CS est porteur du laboratoire commun Systèmes Embarqués pour la Mobilité Autonome SEMA, en partenariat avec la société NXP semiconductors et les laboratoires LAPLACE et LAAS/CNRS (voir le site du SEMA)

Le groupe CS est également à l’origine de nombreux brevets (accessibles gratuitement ici), comme par exemple :

« MULTIPHASE DC TO DC CONVERTERS WITH PHASE SHEDDING, AND SUB-UNITS AND METHODS THEREFOR », Application Number 19306558.8 , NXP USA, Inc. and INSTITUT NATIONAL POLYTECHNIQUE DE TOULOUSE, date de dépôt 03 December 2019 , inventeurs : Loic HUREAU, Marc Michel COUSINEAU.

« DISTRIBUTED INTERLEAVING CONTROL OF MULTIPHASE SMPCS », Application Number 19306559.6 , NXP USA, Inc. and INSTITUT NATIONAL POLYTECHNIQUE DE TOULOUSE, date de dépôt 03 December 2019 , inventeurs : Miguel MANNES HILLESHEIM, Marc Michel COUSINEAU, Eric Pierre ROLLAND, Philippe GOYHENETCHE and Guillaume Jacques Leon AULAGNIER.

« DISTRIBUTED CONTROL OF A VOLTAGE REGULATOR », Application Number 19306578.6, NXP USA, Inc. and INSTITUT NATIONAL POLYTECHNIQUE DE TOULOUSE, date de dépôt 05 December 2019 , inventeurs : Guillaume Jacques Leon AULAGNIER, Miguel MANNES HILLESHEIM, Eric Pierre ROLLAND, Philippe GOYHENETCHE and Marc Michel COUSINEAU.

GATEAU, Guillaume, MEYNARD, Thierry, POSTIGLIONE, Gianluca, et al. Electric power converter. U.S. Patent Application No 16/420,128, 28 nov. 2019.“Multi-Level Inverter Topologies for Medium and High Voltage Applications,”

Odriozola, T.A. Meynard, and A. Lacarnoy, US patent A2000-7629 (APC-0704-US-PSP). (déposants Schneider Electric, CNRS, INPT)

« Détecteur de court-circuit pour transistor de puissance par surveillance du courant de sa grille », Frédéric RICHARDEAU, Jean-Marc BLAQUIERE, François BOIGE, Sébastien VINNAC, FR2011599, 12/11/2020, INSTITUT NATIONAL POLYTECHNIQUE DE TOULOUSE, CENTRE NATIONAL DE LA RECHERCHE SCIENTIFIQUE, UNIVERSITE TOULOUSE III – PAUL SABATIER

« MULTIPHASE DC TO DC CONVERTERS WITH PHASE SHEDDING, AND SUB-UNITS AND METHODS THEREFOR », Application Number 19306558.8 , NXP USA, Inc. and INSTITUT NATIONAL POLYTECHNIQUE DE TOULOUSE, date de dépôt 12/02/2020, inventeurs : Loic HUREAU, Marc Michel COUSINEAU.

« DISTRIBUTED INTERLEAVING CONTROL OF MULTIPHASE SMPCS », Application Number 19306559.6 , NXP USA, Inc. and INSTITUT NATIONAL POLYTECHNIQUE DE TOULOUSE, date de dépôt 12/02/2020, inventeurs : Miguel MANNES HILLESHEIM, Marc Michel COUSINEAU, Eric Pierre ROLLAND, Philippe GOYHENETCHE and Guillaume Jacques Leon AULAGNIER.

« DISTRIBUTED CONTROL OF A VOLTAGE REGULATOR », Application Number 19306578.6, NXP USA, Inc. and INSTITUT NATIONAL POLYTECHNIQUE DE TOULOUSE, date de dépôt 12/02/2020, inventeurs : Guillaume Jacques Leon AULAGNIER, Miguel MANNES HILLESHEIM, Eric Pierre ROLLAND, Philippe GOYHENETCHE and Marc Michel COUSINEAU.

« MODULAR INTERLEAVING TECHNIQUES FOR SCALABLE POWER ELECTRONICS CONVERTER », Application Number 20305395.4, NXP USA, Inc. and INSTITUT NATIONAL POLYTECHNIQUE DE TOULOUSE, date de dépôt 12/02/2020, inventeurs : Miguel MANNES HILLESHEIM, Marc Michel COUSINEAU, Eric Pierre ROLLAND, Philippe GOYHENETCHE and Guillaume Jacques Leon AULAGNIER.

FR 252156 – « PROCEDE DE COMMANDE D’UN CONVERTISSEUR ALTERNATIF-CONTINU DE TYPE MMC, CONVERTISSEUR ALTERNATIF CONTINU DE TYPE MMC ET PRODUIT PROGRAMME D’ORDINATEUR », D. GUEDON, S. CORNET, P. LADOUX, S. SANCHEZ – Co-déposants EDF, CNRS, INPT – Décembre 2020.

Multi-level inverter topologies for medium-and high-voltage applications ; K Odriozola, T Meynard, A Lacarnoy ; US Patent App. 16/883,174

Electric power converter, G Gateau, T Meynard, G Postiglione, G Borghetti, D Falchi, US Patent 10,574,130

| NOM Prénom | Corps / Tutelle | Page Personnelle |

|---|---|---|

| {{statut.name}} | ||

| {{ item.nomprenom }} {{ item.nomprenom }} ({{item.servicecommun1}}) | {{ item.corps }} / {{ item.tutelle }} {{item.statut.toUpperCase()}} | Page web |

Luc BIMMEL soutiendra sa thèse le vendredi 20 février 2026 à 09 h 00 en salle des thèses de l’ENSEEIHT (Amphi C002), au 2 Rue

Daniel GALVIS soutiendra sa thèse le mardi 03 février 2026 à 14 h 00 – salle de thèses C002 à l’ENSEEIHT, sur le sujet : «

Les travaux de PFE Ingénieur ENSEEIHT et de Master Recherche de Camille Bidaud viennent d’être honorés successivement par le 1er Prix « Jeunes » de la SEE

Joseph Kemdeng soutiendra sa thèse le mercredi 17 décembre 2025 à 09h30 – Salle des thèses ENSEEIHT (C002), sur le sujet : Intégration monolithique d’un

Thomas DIAS soutiendra sa thèse le jeudi 20 novembre 2025 à 9h30 – Salle des thèses, ENSEEIHT, sur le sujet : Convertisseur pour station de recharge

Mathis Picot-Digoix soutiendra sa thèse Cifre le vendredi 3 octobre 2025 à 13h30, site de l’ENSEEIHT, salle C002, sur le sujet : Architectures multi-niveaux et

Le 6ème symposium de génie électrique, SGE2025, a eu lieu à Toulouse du 1er au 3 Juillet, au centre de congrès Pierre Baudis. Ce symposium,

Mathis Picot-Digoix à la Session d’ouverture Preview Highlight Poster de l’IEEE Applied Power Electronics Conference and Exposition (APEC), le 17 mars 2025 à Atlanta, USA.

La soutenance de thèse de Damien MICHEZ intitulée : « Fabrication et caractérisation de transistor à effet de champ en diamant en vue de l’augmentation du